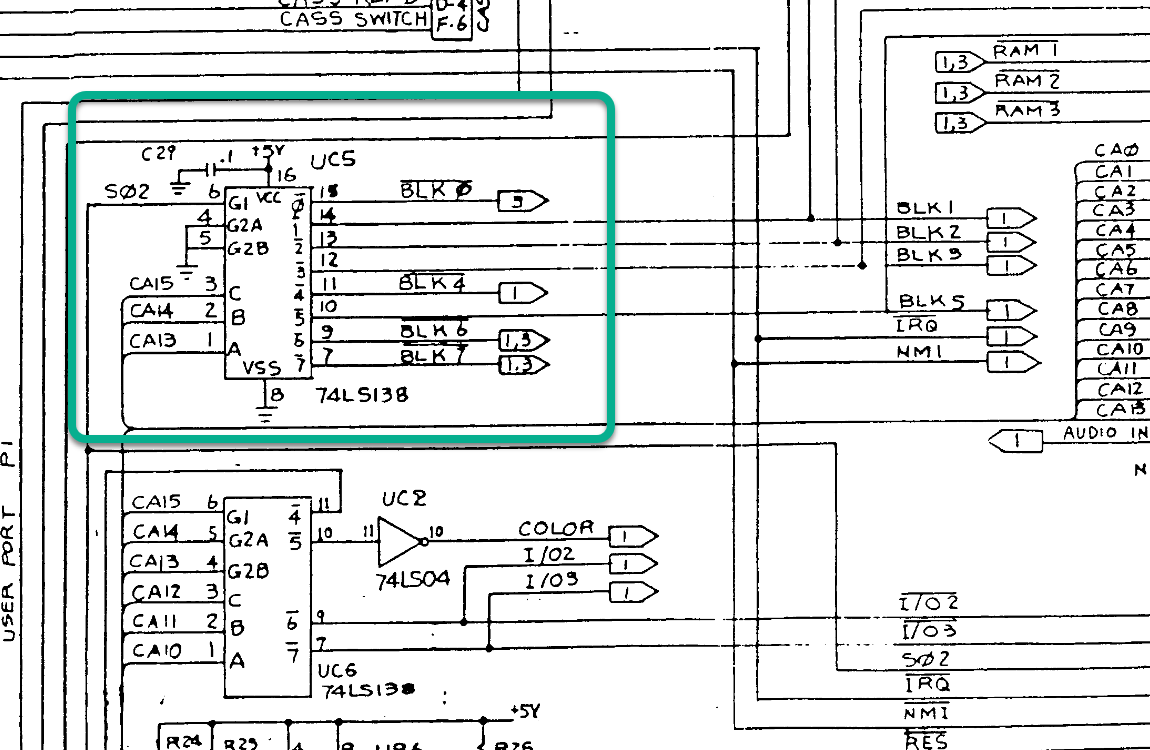

In the VIC 20 there is a 74LS138 which is the main chip select decoder logic. This splits the 64k addressable space into 8k chunks named BLK0, BLK1, BLK2, BLK3, etc.

BLK0 is the main unexpanded memory of the VIC 20. It has 5k of memory with a hole in the range $0400 - $0FFF. This memory is addressable by the VIC chip. The missing part is routed to the expansion port directly. IF expanded as with the Super Expander BASIC can use this memory, but the VIC chip cannot reach it, due to the interleaved design of the architecture. 6502 and VIC takes turn on accessing the bus and the cartridge expansion is hidden from the VIC chip though a set of buffers.

BLK1, BLK2, and BLK3 is plain SRAM from $2000 - $7FFF. This is expandable through the cartridge expansion port.

BLK4 is IO and Character ROM. Partly accessible to the VIC chip.

BLK5 at $A000 - $BFFF is the cartridge memory area. At start the VIC 20 looks for a signature in the beginning of this area. If found it continues executing from this area.

BLK6 and BLK7 is for Kernal and BASIC ROM.

FATVIC Memory expansion

One idea with FATVIC was to remedy the problem with the hole at $0400 - $0FFF.

The ECP-5 FPGA used has 64k of internal memory so it is trivial to expand this.

However. We need to route the chip select signal of BLK0 from the main system to the FATVIC.

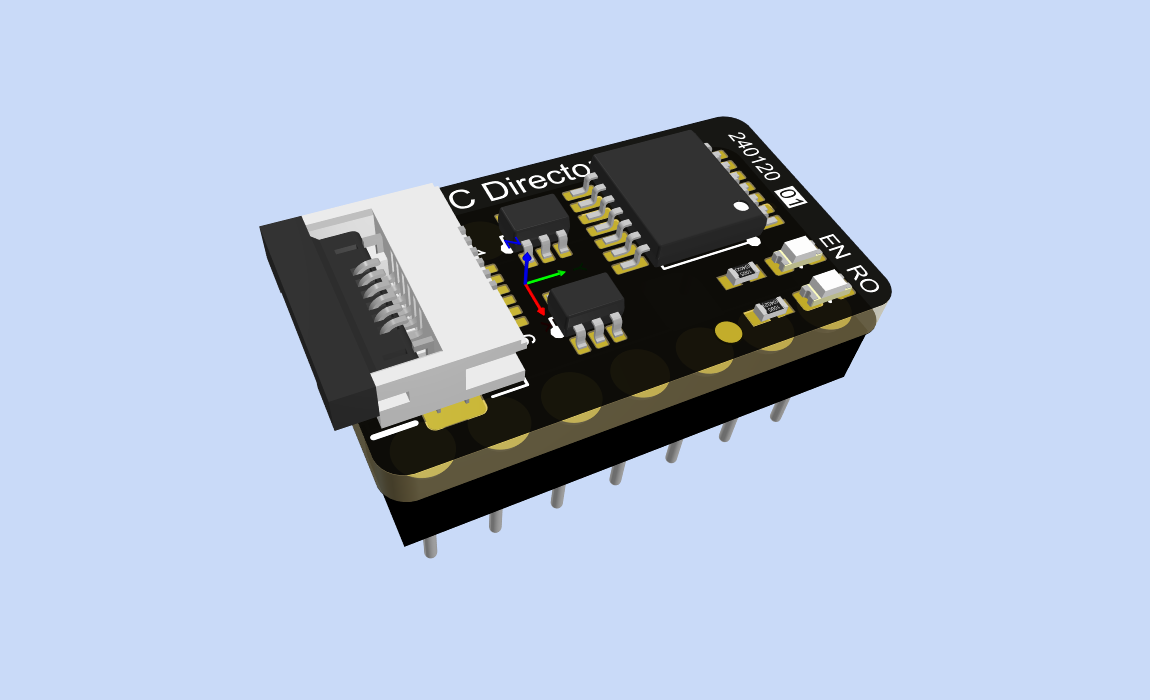

This is where the FATVIC Director comes into play. It replaces the 74LS138 and has a FFC cable between it and the FATVIC.

FATVIC can via software enable and disable this feature. When enabled BLK0 into the main board is totally disabled (which also disables the access to the 3k chip select signals RAM1, RAM2 and RAM3 on the cartridge expansion port.

If the FATVIC director is disabled everything works as normal.